### Design Of A Single Stage Source Coupled CMOS VCO using 180nm Technology

Ankit Gupta<sup>1</sup>, R. S. Gamad<sup>2</sup>

<sup>1,2</sup>(Department of Electronics & Instrumentation Engineering, SGSITS INDORE, MP,India-452003)

### ABSTRACT

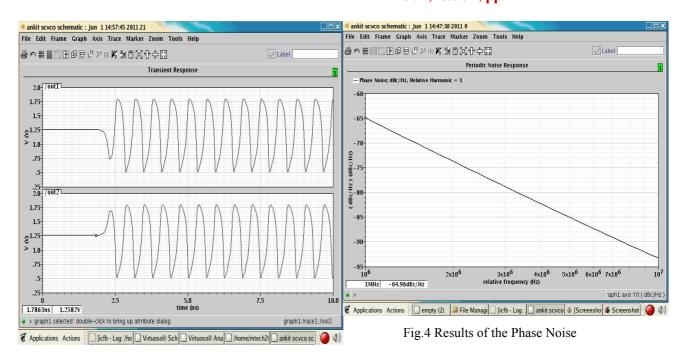

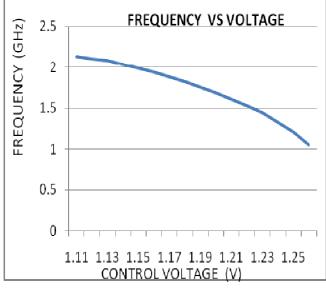

A single stage source coupled Complementary Metal Oxide Semiconductor Voltage Controlled Oscillator (CMOS VCO) is designed in this paper. The design is implemented in Cadence environment with high oscillation frequency and low power consumption. This design is a single stage and it has low phase noise because author has reduced noise sources. Oscillation frequency of the designed VCO is ranges from 1.052 GHz to 2.136 GHz. The circuit is simulated using 180nm UMC Technology. Simulation results are reported that the phase noise is -64.96dBc/Hz@1MHz and power consumption is 6.951 mW with 2.136 GHz oscillation frequency and 1.8 V supply voltage. Present results are compared with earlier published work and improvements are observed. Keywords - Cadence, Low power, Low Phase

Noise, Source coupled VCO

### I. INTRODUCTION

VCO is the heart of the Phase Locked Loops (PLLs) and data recovery circuits which is widely used in wireless and wire-line communication system. In recent years, the CMOS LC-tank oscillators have shown an excellent phase noise performance with Low power consumption because of a relatively high quality factor [1]. The oscillation frequency of the ring oscillator is inversely proportional to the number of delay stages. It is desirable to design a two stage ring VCO to satisfy Barkhausens criteria. Several novel delay cells have been proposed to compose the two stage ring VCO [2][3]. But much extra power is needed to provide an excess phase shift. The output signal swing is reduced in order to place the complex poles in front of the zero. Consequently, the phase noise performance of this two stage ring VCO is relatively poor [4].

### **II. INDENTATIONS AND EQUATIONS**

The Frequency of Oscillation is given as [7]:

Initially we have mathematical analysis

$$F_{osc} = 1/2. \Delta t = I_d / 4.C. V_{th}$$

(1)

where  $F_{osc}$ = the frequency of oscillation.

The average power dissipated by the VCO is

$P_{avg} = VDD. I_{avg} = VDD. I_D$ (2)

Where, VDD = supply voltage and  $I_D =$  drain current through supply voltage

### **III. FIGURES AND TABLES**

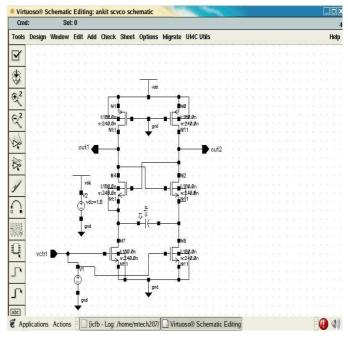

VCO

# Ankit Gupta, R. S. Gamad/ International Journal of Engineering Research and Applications(IJERA)ISSN: 2248-9622Www.ijera.comVol. 1, Issue 2, pp.122-124

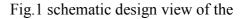

Fig.2 Simulation result of the output VCO

Fig.3 Graphical representation of frequency Vs control Voltage

Table 1: Comparison of present work with

earlier reported work

| parameter | Ref[1]      | Ref[5]      | This design        |

|-----------|-------------|-------------|--------------------|

| Operating |             |             |                    |

| Voltage   | 1.8V        | 3.3V        | 1.8V               |

| Techno.   | 0.18µm      | 0.35µm      | 0.18µm             |

| (CMOS)    | (CMOS       | (CMOS       | (CMOS              |

|           | Techno.)    | Techno.)    | Techno.)           |

| Power     |             |             |                    |

| Consump.  | 17mW        | 15.5mW      | 6.951mW            |

| Operating |             |             |                    |

| Frequency | 2.5-5.2 GHz | 2.5-5.2 GHz | 1.052-2.136<br>GHz |

| Phase     | -90.1dBc/Hz | -135dBc/Hz  | -64.96dBc          |

| Noise     |             |             | /Hz                |

| (dBc/Hz)  | @1MHz       | @ 1MHz      | @1MHz              |

| Number    | 2           |             | 1                  |

| of stages |             |             |                    |

### **IV.** CONCLUSION

This paper presents a design of a low power, low phase noise 2.136 GHz CMOS VCO using 180 nm UMC Technology. Finally authors have compared the presented results with earlier published work

## Ankit Gupta, R. S. Gamad/ International Journal of Engineering Research and Applications(IJERA)ISSN: 2248-9622Val. 1Issue 2Val. 1Issue 2International Journal of Engineering Research and Applications

and improvement observed in this result as given in table1. The simulation results of this design shows that the proposed VCO could achieve high oscillation frequency with the better phase noise performance and low power consumption. This design is suitable for wireless applications.

### ACKNOWLEDGEMENTS

This work has been carried out in SMDP VLSI laboratory of the Electronics and Instrumentation Engineering Department of Shri G. S. Institute of Technology and Science, Indore, India. This SMDP VLSI project is funded by Ministry of Information and Communication Technology, Government of India. Authors are thankful to the Ministry for the facilities provided under this project.

### REFERENCES

- Wei-Hsuan Tu, Jyh-yjhyeh, Hung chieh Tsai and chorng – Kuang wang, "A1.8V

2.5-5.2 GHz CMOS Dual-input two stage Ring VCO", Asia- pacificconfrernce an advanced system IC, IEEE Aug. 2004

- [2]. Hormoz Djahanshahi and C. Andre,

"Differential CMOS circuit for 622 MHz 933 MHz CDR application", IEEE J.

solid-state circuits, June 2000.

- [3]. William shing Tak Yan, "A 900 MHz CMOS Low Phase Noise voltage controlled ring oscillator", IEEE transaction on circuits &systems, Feb. 2001.

- [4]. Seema Butala Anand and Behzad Razavi,

"A CMOS Clock recovery circuit for 2.5 Gb/s NRZ data", IEEE J. solid state circuits Mar, 2001.

- [5]. Honghui Deng Yongsheng Yin Goaming Du, "Phase Noise Analysis and Design of

Vol. 1, Issue 2, pp.122-124

CMOS Differential Ring VCO", IEEE 2009.

- [6]. Behzad Razavi, "Deign of Analog CMOS Integrated Circuits", Book by Tata MC Graw-Hil Edition, 2000.

- [7]. R. Jacob Baker, Harry W. Li and David E.

Boyce, "CMOS Circuit Design, Layout, Simulation", IEEE Press Series on Microelectronic System.

- [8]. Huang Shizen, Lin Wei, wang Yutong, Zheng Li, " Design Of A Voltage-Contronlled Ring Oscillator Based On MOS Capacitances". International MultiConfrence of Engineers and Scientists 2009 Vol. II IMECS 2009, March 2009 Hong Kong.

- [9]. Rui Tao, Manfred Berroth, "5 GHz Voltage Controlled Ring Oscillator Using Source Capacitively Coupled Current Amplifier", IEEE 2003.